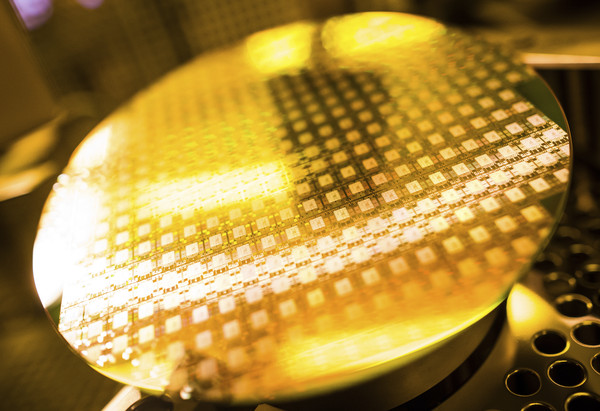

▲新思科技推出DesignWare IP解決方案。(圖/達志影像)

記者周康玉/台北報導

新思科技近日宣布其用於台積電7奈米製程技術的DesignWare邏輯庫、嵌入式記憶體、介面和類比IP已獲得超過250個設計的選用(design wins);且有近30家半導體領導廠商選擇新思科技DesignWare IP解決方案,作為行動、雲端運算及汽車等各式應用提供高效能、低功耗的系統晶片(SoCs)。

[廣告] 請繼續往下閱讀.

由於達成多項客戶矽晶設計成功,DesignWare IP獲得廣泛的採用,也因此設計人員在整合IP時能更具信心,並大幅降低SoC整合的風險。

台積電設計建構管理處資深處長Suk Lee表示,台積電與新思科技就多項製程進行密切合作,凸顯了雙方致力於為設計人員提供IP,以協助其解決關鍵設計的挑戰,並快速進入量產。

新思科技IP行銷副總裁John Koeter指出,為了滿足當前AI工作量(AI workloads)、影片流量以及雲端和邊緣資訊密集運作的需求,設計人員仰賴新思科技在最先進的高效能FinFET製程中,提供經過驗證的IP解決方案。用於台積電7奈米製程、通過矽晶驗證的DesignWare獲得廣大客戶採用而取得廣泛驗證,能讓設計人員以更少的風險推出差異化產品,加快上市時程。